Placa Aceleradora Spartan Edge

A Spartan Edge Accelerator Board (abreviada como SEA Board) é uma placa de desenvolvimento FPGA leve, baseada no chip Xilinx Spartan-7 e que segue o fator de forma de shield Arduino. Assim, você pode usá-la como um shield Arduino para controlar um LCD e uma câmera ou como uma placa de desenvolvimento FPGA independente. Além disso, com a ajuda do chip ESP32 integrado, a placa SEA também adiciona funções de WiFi e Bluetooth ao seu Arduino.

Spartan-7 é o chip FPGA mais novo e mais econômico entre a família de FPGAs da Xilinx, oferecendo a melhor relação desempenho por watt da categoria.

Além disso, fornecemos APIs FPGA completas para Arduino, o que significa que usuários de Arduino podem usar as funções de FPGA sem saber nada sobre FPGA. Esta placa ampliará a capacidade do Arduino de várias maneiras, como processamento simples de imagens e aplicações de visão computacional, criptografia e descriptografia de sinais, e amostragem e processamento de sinais.

Recursos

Processamento de imagem em alta velocidade

- Interface mipi e mini HDMI integradas

- Suporta câmera Raspberry Pi v1.0 (OV5640)

- Suporte máximo para transmissão de imagem a 30fps

Internet das Coisas criptografada

- WiFi e Bluetooth para IoT com ESP32

- Suporta AWS, Azure e outros serviços em nuvem

- Suporta algoritmo de criptografia por software

Múltiplas extensões de portas de E/S

- 20 portas de E/S estendidas definidas pelo usuário (modo independente)

- 10 portas de E/S estendidas definidas pelo usuário (modo shield Arduino)

- APIs FPGA completas para Arduino

Módulos funcionais integrados

- ADC e DAC de 8 bits

- Acelerômetro e giroscópio de 6 eixos

- 2 LEDs RGB de usuário e botões

Dois modos de desenvolvimento personalizados

- Modo Shield Arduino

- Modo FPGA Independente

Observação: Os usuários podem escolher diferentes conectores de pinos de acordo com suas necessidades e soldar os pinos conforme as necessidades de desenvolvimento.

Usuários-alvo

- Desenvolvedores Arduino

- Desenvolvedores de IoT

- Desenvolvedores de FPGA

Casos de aplicação

- Engenharia Vivado com entrada de câmera MIPI e saída HDMI

- Caso de referência com LED onboard, DIP switch, ADC e DAC

- Caso com giroscópio onboard

- Fornece expansão GPIO/UART/ADC/DAC/RGB-LED para Arduino

- Caso de gerador de sinal (requer configuração do Arduino)

- Caso de gerador de sinal controlado por ESP32

- Uso do caso com a plataforma IoT AWS GreenGrass

- Caso de reconhecimento de cores e rastreamento de objetos

- Caso de reconhecimento gráfico (reconhecimento de triângulo, círculo e quadrado)

- Caso de reconhecimento de caracteres digitais

- Implementação do algoritmo de criptografia e descriptografia AES em FPGA

- Implementação do algoritmo PID em FPGA

Novas aplicações serão atualizadas.............

Para mais recursos de casos, visite esta página no Github.

Especificações

Parâmetro | Valor |

FPGA | |

Chip FPGA | Spartan-7 XC7S15 |

Células lógicas | 12,800 |

Slices | 2000 |

Flip-Flops de CLB | 16000 |

RAM distribuída máx. (Kb) | 150 |

Block RAM/FIFO c/ ECC (36 kb cada) | 10 |

RAM distribuída máx. (Kb) | 150 |

RAM de bloco total (Kb) | 360 |

RAM distribuída máx. (Kb) | 150 |

Blocos de gerenciamento de clock (1 MMCM + 1 PLL) | 2 |

Slices DSP | 20 |

Wireless | |

Chip wireless | Espressif ESP32-D0WDQ6 |

WiFi | 802.11 b/g/n 2.4GHz |

Bluetooth | Bluetooth 4.1 com BLE |

Periférico | |

Vídeo | Mini HDMI x1 |

Câmera | Interface CSI/MIPI x1 (compatível com Raspberry Pi Camera V1 - OV5640) |

Cartão SD | 20 |

Slices DSP | Slot para cartão Micro SD/TF x1 |

FPGA GPIO | Conector de 10 pinos (IO9~IO0) |

Arduino GPIO | Conector de 32 pinos (fator de forma Arduino) |

Grove | Conector Grove x2 (I2C/D2) |

LED | LED monocromático x2 |

Botão | Boot x1 |

Switch | Chave de modo de alimentação x1 |

Alimentação | |

Tensão de operação | 5V |

Tensão de IO | 5V |

Modo de alimentação | USB Tipo C 5V |

Outros | |

ADC | ADC1173 de 8 bits |

Acelerômetro e giroscópio | LSM6DS3TR de 6 eixos |

A tensão de IO do shield SEA é 5V, e a tensão de IO do FPGA é 3,3V, então fizemos um divisor de tensão para tornar a tensão dos IOs compatível. A tensão de IO de 3,3V da série SAM D21 será menor que 3,3V após a divisão de tensão, o que não é suficiente para acionar o IO do FPGA. Portanto, no momento, a placa de desenvolvimento SEA só oferece suporte a placas Arduino com IO de 5V, como Arduino UNO e Seeeduino V4.2.

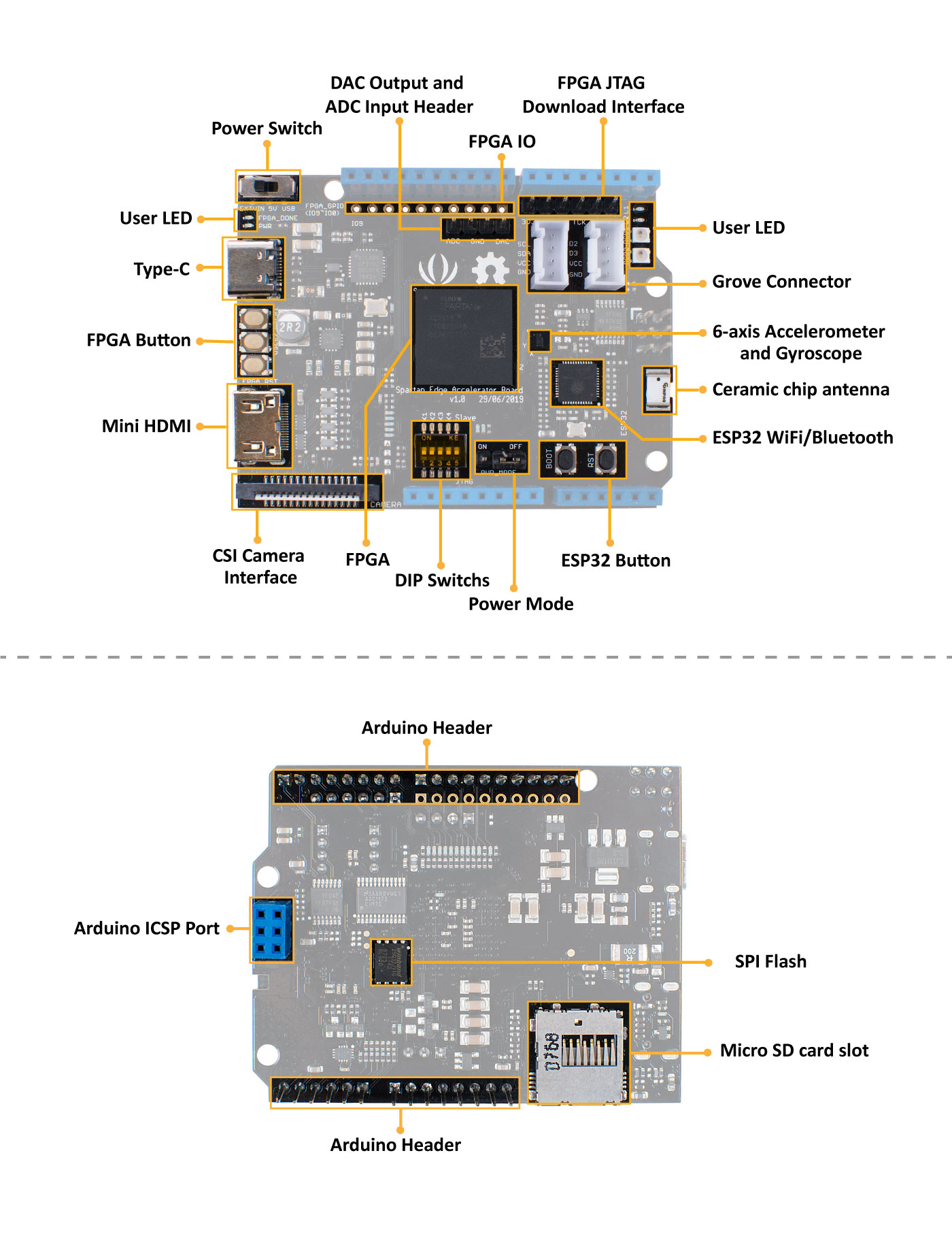

Visão geral de hardware

Número | Detalhe |

1 | FPGA : XC7S15-1FTGB196C |

2 | WiFi/Bluetooth : ESP32-D0WDQ6 |

3 | Acelerômetro e giroscópio de 6 eixos : LSM6DS3TR |

4 | DAC : DAC7311IDCKR |

5 | Buck-DCDC : TPS62130 |

6 | USB-para-UART : CP2102-GMR |

7 | USB : Tipo-C |

8 | Mini HDMI |

9 | Interface CSI :Câmera MIPI (compatível com Raspberry Pi Camera V1 - OV5640) |

10 | Cabeçalho Arduino : Compatível com Arduino UNO |

11 | DIP Switchs : |

12 | Botão do ESP32 :Boot e RST |

13 | Botão do FPGA :USER1 USER2 FPGA_RST |

14 | LED de usuário: L1/L2/RGB1/RGB2 |

15 | Interruptor de alimentação : |

16 | Modo de alimentação: |

17 | Cabeçalho de saída do DAC e entrada do ADC |

18 | FPGA IO : IO9~IO0 |

19 | Interface de download JTAG do FPGA |

20 | Conector Grove : 1x I2C; 1x D2&D3 |

21 | Antena de chip cerâmica |

22 | ADC : ADC1173 |

23 | SPI Flash : W25Q32JVZPIG |

24 | Switch analógico :DG2788A |

25 | LDO : XC6221B102MR |

26 | LDO : RT9013-18GB |

27 | LDO : CJ1117-3V3 |

28 | Slot para cartão SD : Cartão Micro SD/TF |

Primeiros Passos

A Spartan Edge Accelerator Board pode funcionar em dois modos:

- Modo Shield Arduino

- Modo Independente

Em resumo, ela pode funcionar como um shield Arduino para trazer recursos de FPGA e Wireless ao Arduino, e também pode funcionar como uma placa de desenvolvimento FPGA sem um Arduino.

Modo de shield Arduino

Neste wiki, usamos o Seeeduino V4.2; você também pode usar o Arduino UNO, eles são totalmente compatíveis entre si.

Hardware

Materiais necessários

- Seeeduino V4.2 x1

- Spartan Edge Accelerator Board x1

- Cartão Micro SD ou cartão TF x1

- Cabo de dados USB Type C x1

Conexão de hardware

- Etapa 1. Insira o cartão Micro SD ou cartão TF no slot de cartão SD

- Etapa 2. Conecte a SEA Board ao Arduino

- Etapa 3. Use um dos três métodos a seguir para alimentar o sistema

Porta de alimentação | Tensão de entrada | Posição do interruptor de alimentação | Posição do modo de alimentação |

Alimentado pela porta USB Type C da SEA board | 5V CC | USB | ON |

Alimentado pela porta micro USB do Seeeduino V4.2 | 5V CC | - | ON |

Alimentado pela porta CC do Seeeduino V4.2 | 8~17V CC | 5V | ON |

Você também pode alimentar a SEA board e o Arduino ao mesmo tempo, mas certifique-se de que você definiu a posição do modo de alimentação como OFF. Só então a alimentação do sistema será isolada e você poderá alimentar o Arduino e a SEA board separadamente.

Inicialização do ESP32 da Spartan Edge Accelerator Board

Primeiro, para trabalhar com Arduino, devemos carregar o bitstream (Lógica FPGA) do cartão SD para o FPGA (xc7s15) on‑board. A biblioteca a seguir mostrará como fazer isso via ESP32 on‑board.

uma biblioteca para Spartan Edge Accelerator Board

O objetivo desta biblioteca é carregar o bitstream (Lógica FPGA) do cartão SD para o FPGA (xc7s15) on‑board pelo ESP32 on‑board.

O ambiente de desenvolvimento de software é o Arduino IDE com suporte a placas ESP32.

Desde a versão 1.6.4, o Arduino permite a instalação de pacotes de plataforma de terceiros usando o Boards Manager. Temos pacotes disponíveis para Windows, Mac OS e Linux (32 e 64 bits).

- Instale a versão atual do Arduino IDE upstream no nível 1.8 ou posterior. A versão atual está no site do Arduino.

- Inicie o Arduino e abra a janela de Preferences.

- Insira

https://dl.espressif.com/dl/package_esp32_index.jsonno campo Additional Board Manager URLs. Você pode adicionar vários URLs, separando‑os com vírgulas. - Abra o Boards Manager no menu Tools > Board e instale a plataforma esp32 (e não se esqueça de selecionar sua placa ESP32 no menu Tools > Board após a instalação).

- selecione tool->board->DOIT ESP32 DEVKIT

Link de lançamento estável: https://dl.espressif.com/dl/package_esp32_index.json

Link de lançamento de desenvolvimento: https://dl.espressif.com/dl/package_esp32_dev_index.json

Se você quiser mais detalhes, pode clicar no link

Uso da biblioteca

- 1. Baixar a ESP32 Boot Library

Em seguida, adicione esta biblioteca ao seu Arduino IDE.

Se você não souber como instalar a biblioteca, por favor verifique:

Installing Additional Arduino Libraries

Você pode encontrar duas pastas de exemplos nesta biblioteca

Exemplo | Descrição |

01LoadDefaultBitstream | Este exemplo carregará o arquivo /overlay/default.bit do cartão SD para o FPGA |

02LoadConfigBitstream | Este exemplo lerá um arquivo no formato ini /board_config.ini no cartão SD e então carregará no FPGA o bitstream especificado pelo valor da chave overlay_on_boot. |

- 2. Preparar o cartão SD

2.1 Formate o cartão SD com o sistema de arquivos FAT16/FAT32.

2.2 Crie uma subpasta de nível superior chamada overlay no cartão SD.

2.3 Coloque seus arquivos de bitstream ou bitstream de exemplo (devem ter a extensão .bit) na pasta overlay.

O bitstream de exemplo: extensão de GPIO controlada pela interface SPI, com suporte a ADC/DAC/RGB‑LED, veja o código‑fonte.

2.4 Se você executar o exemplo 01LoadDefaultBitstream, renomeie o arquivo de bitstream em overlay para default.bit.

2.5 Se você executar o exemplo 02LoadConfigBitstream, coloque o board_config.ini na pasta raiz do cartão SD.

2.6 Insira o cartão SD na Spartan (Edge Accelerator) Board.

-

3. Fazer upload do exemplo

3.1 Conecte a Spartan Board ao PC através de um cabo USB Type‑C e instale o driver USB232 (chip CP2102).

3.2 Coloque o interruptor de alimentação (perto do slot USB Type‑C) para o lado USB para ligar a placa.

3.3 Abra um dos exemplos da biblioteca pelo Arduino IDE.

3.4 Verifique as configurações de Board & Port no Arduino IDE conforme descrito na última seção.

3.5 Pressione o botão 'BOOT' na Spartan Board por mais de 1 segundo para forçar o ESP32 a entrar no modo Bootloader.

3.6 Pressione o botão 'Upload' no Arduino IDE para fazer upload do exemplo (binário compilado) para o ESP32. -

4. Executar o exemplo

4.1 Certifique‑se de que o DIP‑switch K5 on‑board (o último) esteja no lado Slave (ON), o que permite a programação do FPGA por outro dispositivo (MCU).

4.2 Pressione o botão 'RST' na Spartan Board para iniciar o exemplo.

4.3 Alguns segundos após a inicialização do exemplo, o LED FPGA_DONE (cor vermelha) na placa acenderá.

Exemplo de IO da Spartan Edge Accelerator Board

Em seguida, o tutorial a seguir mostrará como controlar os recursos GPIO/ADC/DAC/RGB‑LED da Spartan Edge Accelerator Board com Arduino.

- Baixe a IO Example Library:

- Adicione esta biblioteca ao seu Arduino IDE. Se você não souber como instalar a biblioteca, por favor verifique:

Installing Additional Arduino Libraries

-

Vá até a pasta

examples, escolha qualquer exemplo, dê um duplo clique no arquivo .ino. -

Faça upload da demonstração. Se você não souber como fazer upload do código, por favor verifique How to upload code.

Modo Stand-alone

Hardware

Materiais necessários

Basta alimentar a Spartan Edge Accelerator Board via cabo USB Type C.

Software

A Spartan Edge Accelerator Board também pode funcionar como uma tradicional placa de desenvolvimento FPGA. O tutorial a seguir mostrará como usá‑la no modo stand‑alone.

Nesta seção, você aprenderá sobre os recursos do modo Project para criação de projeto, gerenciamento de arquivos‑fonte, análise de projeto, definição de restrições e gerenciamento das execuções de síntese e implementação. Isto pode ser usado como uma referência rápida.

Antes de tudo, você deve baixar a biblioteca de tutoriais do Vivado; precisaremos de alguns arquivos‑fonte.

-

Etapa 1: Criando um projeto

Iniciando o Vivado

Criando um novo projeto

-

Depois que o Vivado abrir, selecione Create Project na página Getting Started.

-

Clique em Next no assistente New Project

-

Especifique o nome e o local do projeto (selecione “Create project subdirectory” para criar uma pasta para o seu projeto)

-

Clique em Next.

-

Selecione RTL Project como Project Type e clique em Next. (selecione Do not specify sources at this time e adicione seus arquivos logo em seguida)

(O Vivado Design Suite permite diferentes pontos de entrada de design dependendo dos tipos de arquivos‑fonte e das tarefas de design. Você pode escolher o tipo de projeto adequado.)

-

Selecione o componente xc7s15ftgb196-1 para o projeto e clique em Next, como mostrado na figura 1.

-

Clique em Finish

O Vivado IDE abre o project_tutorial no layout padrão, como mostrado na figura 2.

O Flow Navigator mostra claramente o processo básico de projeto.

As Sources são compostas por Constraints, Simulation Sources e Utility Sources.

O Design Runs cria synth_1 e impl_1 por padrão.

O status de execução do Vivado é exibido no canto superior direito.

-

Passo 2: Adicionar e Criar Seus Arquivos

neste passo, adicionamos test.v , test_pin.xdc , test_sim.v em nosso projeto. Esses arquivos estão localizados em diferentes pastas de vivado_tutorial/vivado_tutorial.srcs

-

Clique em Add Sources em PROJECT MANAGER do Flow Navigator para adicionar o arquivo RTL.

-

Selecione Add or create design sources e clique em Next.

-

Clique no botão e selecione opções ou clique diretamente nas opções para adicionar ou criar arquivos, como mostrado na figura 3.

- Aqui, adicionamos arquivos RTL diretamente. Selecione Add Files e adicione o arquivo test.v no seu diretório, como mostrado na figura 4.

-

Clique em Finish.

-

Clique em Add Sources em PROJECT MANAGER do Flow Navigator novamente para adicionar o arquivo de constraints.

-

Selecione Add or create constraints e clique em Next.

-

Clique em Add Files e adicione seu arquivo de constraints test_pin.xdc , como mostrado na figura 5

-

Clique em Finish.

-

Clique em Add Sources em PROJECT MANAGER do Flow Navigator novamente para adicionar o arquivo de simulação.

-

Selecione Add or create simulation sources e clique em Next.

-

Clique em Add Files e adicione seu arquivo de simulação test_sim.v , como mostrado na figura 6

-

Clique em Finish.

Finalmente, o arquivo que adicionamos aparecerá em Sources, como mostrado na figura 7.

-

Passo 3: Elaborar o Projeto RTL

O Vivado IDE inclui um ambiente de análise RTL e customização de IP. Há também várias RTL Design Rule Checks (DRCs) para examinar maneiras de melhorar o desempenho ou o consumo de energia no projeto RTL.

-

Selecione Open Elaborated Design no Flow Navigator para elaborar o projeto.

-

Certifique-se de que o menu suspenso Layout Selector na barra de ferramentas principal esteja com Default Layout selecionado. O Elaborated Design habilita várias visualizações de análise, incluindo uma RTL Netlist, Schematic e Graphical Hierarchy. As visualizações têm um recurso de seleção cruzada, que ajuda você a depurar e otimizar o RTL.

-

Explore a hierarquia lógica na janela RTL Netlist e examine o Schematic. Você pode percorrer o schematic clicando duas vezes nas células para avançar na hierarquia, ou usando comandos como Expand Cone ou Expand/Collapse no menu pop-up do Schematic.

-

Selecione qualquer instância lógica no Schematic e clique com o botão direito para selecionar os comandos Go to Source ou Go to Definition.

-

Clique na janela Messages na parte inferior do Vivado IDE e examine as mensagens.

-

Clique no botão Collapse All na barra de ferramentas de Messages.

-

Expanda o Elaborated Design e as mensagens, como mostrado na figura 8.

- Clique em um dos links e o Text Editor abre o arquivo-fonte RTL com a linha relevante destacada.

- Feche as janelas do Text Editor.

- Feche o Elaborated Design clicando no X no lado direito do banner da janela Elaborated Design e clique em OK para confirmar.

-

Passo 4: Usando o IP Catalog

O Xilinx IP Catalog fornece acesso aos recursos de configuração e geração de IP do Vivado. Você pode classificar e pesquisar o Catalog de várias maneiras. O IP pode ser customizado, gerado e instanciado.

-

Clique no botão IP Catalog no Flow Navigator, em Project Manager.

-

Navegue pelo IP Catalog para examinar as várias categorias e capacidades de filtragem de IP.

-

Escolha o IP correspondente e realize customização nativa e configuração do IP dentro da ferramenta e selecione OK

-

Feche a aba do IP Catalog clicando no X na aba da janela.

-

Passo 5: Executar a Simulação Comportamental

O Vivado IDE integra o Vivado Simulator, que permite adicionar e gerenciar fontes de simulação no projeto. Você pode configurar opções de simulação e criar e gerenciar conjuntos de fontes de simulação. Você pode executar simulação comportamental em fontes RTL antes da síntese.

- No Flow Navigator, em Project Manager, clique no comando Settings. A caixa de diálogo Settings é aberta com Project Settings na parte superior e Tool Settings abaixo disso, como mostrado na figura 9.

- Examine as configurações disponíveis na página Simulation e clique em Cancel para fechar a caixa de diálogo.

- Clique no comando Run Simulation no Flow Navigator e, em seguida, clique em Run Behaviora Simulation no submenu, como mostrado na figura 10.

- Arraste a barra para a esquerda e use essas ferramentas para dar zoom in ou zoom out para ver a imagem apropriada, como mostrado nas figuras 11 e 12.

- Clique em X no canto superior direito da figura 13 e clique em OK para fechar a SIMULATION.

-

Passo 6: Revisar as Configurações do Design Run

Design runs são uma maneira de configurar e armazenar as muitas opções disponíveis nas diferentes etapas do processo de síntese e implementação. Você pode configurar essas opções e salvar as configurações como estratégias a serem usadas em execuções futuras.

-

No Flow Navigator, em Project Manager, clique no comando Settings.

-

Selecione a página Synthesis em Project Settings. Para uma descrição completa dessas opções, consulte o Vivado Design Suite User Guide: Synthesis(UG901).

-

Selecione a página Implementation em Project Settings. Para uma descrição completa dessas opções, consulte o Vivado Design Suite User Guide: Implementation(UG904).

-

Passo 7: Sintetizar e Implementar o Projeto

Após configurar as opções de run de síntese e implementação, você pode run synthesis e run implementation em Design Runs ou clicar no botão ou clicar nos botões correspondentes no Flow Navigator para fazer isso. O status de execução do Vivado é exibido no canto superior direito enquanto estiver sintetizando e implementando.

Para este tutorial, executaremos essas etapas em Design Runs.

- Clique com o botão direito em syth_1 e selecione Launch Runs, como mostrado na figura 14.

- Clique em ok e o status de execução é exibido no canto superior direito, como mostrado na figura 15.

- Clique em Open Synthesized Design para mais projeto e análise. Você pode ver Report Timing Summary , Report Utilization e outros, como mostrado na figura 16.

- Execute Implementation da mesma forma, como mostrado na figura 17.

- Clique em Open implemented Design para ver relatórios após a implementação

-

Passo 8: Gerar um Arquivo Bitstream

Após Implementing the Design, podemos ver synthesis e implement Complete em Design Runs, como mostrado na figura 18.

Clique em Generate Bitstream no Flow Navigator.

-

Passo 9: Baixar o arquivo

Após Generate Bitstream, você tem duas maneiras de carregar o arquivo para o FPGA.

Você pode usar a interface JTAG (no canto superior direito da figura 19) para carregar o arquivo bit no FPGA no Vivado, ou usar o ESP32 (no canto inferior direito da figura 19) para carregar o arquivo bit no FPGA.

Siga as etapas abaixo para carregar o bitstream no FPGA através da interface JTAG

-

Ligue a placa e conecte o Platform Cable USB II (ou cabo compatível).

-

Clique em Open Target e Auto Connect no Flow Navigator.

-

Depois de conectar à placa com sucesso, clique em Program Device, escolha o arquivo bit e clique em Program, como mostrado na figura 20.

-

Após baixar o arquivo bit, o LED FPGA_DONE acenderá.

Neste projeto, se você pressionar qualquer tecla ou ambas (USER1 e USER2), o LED L1 apagará.

Visualizador Online do Esquemático

Recursos

- [PDF] Spartan-7 FPGAs Datasheet

- [PDF] ESP32 Datasheet

- [PDF] Spartan-Edge-Accelerator-Board Eagle File

Suporte Técnico e Discussão sobre o Produto

Obrigado por escolher nossos produtos! Estamos aqui para oferecer diferentes formas de suporte e garantir que sua experiência com nossos produtos seja a mais tranquila possível. Oferecemos vários canais de comunicação para atender a diferentes preferências e necessidades.